Project background and feasibility analysis

1. Project name, main content of the project and current progress

Project name: Frequency domain fast capture of baseband pseudo-code of satellite navigation system;

The main content of the project: the use of FPGA design to achieve a fast frequency domain acquisition algorithm for GNSS signals.

Current progress: With mature algorithm structure and simulation test results, the implementation of related modules begins.

2. Discussion of key technologies and innovations of the project

Innovation point (1): Based on the FFT, the cyclic correlation value of the pseudo code sequence is calculated in the frequency domain. At each Doppler shift, the correlation result is calculated simultaneously for all code delays. Compared with the traditional method of directly calculating the local and received signal correlation values, the operation time is short. For the C/A code, it is only necessary to receive a pseudo-code period (1ms) signal to estimate the code phase; traditional serial correlation, moving up to half a chip at a time, complete a correlation operation, search The entire code period requires a minimum of 2046 movements.

Innovation point (2): The FFT operation requires that the number of data used is an integer power of 2. In general, A/D cannot satisfy the integer power of 2 in one code period. This project completes the matching of data through an average downsampling technique.

Innovation point (3): When the sampled data is one code period, half of the calculation amount can be reduced by processing the single sideband data. Although only the first half of the points can be found after IFFT, these points contain almost all the information.

Key Technology (1): Implementation of FFT

Key Technology (2): Average Downsampling Completes Data Matching

3. Technical maturity and reliability discussion

At present, the algorithm is completed by MATLAB on a general-purpose PC, which proves that the algorithm can not only capture the satellite navigation signals effectively, but also greatly improves the speed compared with the traditional methods, which reduces the workload and complexity of the calculation to a certain extent.

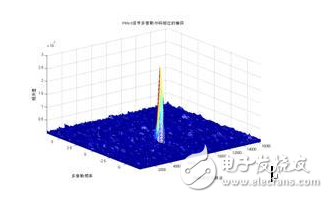

The figure below shows the actual satellite capture results:

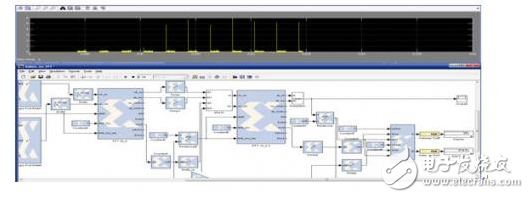

In order to realize the smooth transplantation of the algorithm on the FPGA platform, some hardware co-simulation work was performed under the Simulink by System Generator. The development board is the seed-fem025 of Hezhongda Company, and the FPGA chip is Virtex-4 SX25. Because the hardware resources required for the co-simulation of the whole system hardware are insufficient, the hardware co-simulation sub-module is performed.

The results of the software simulation are as follows:

The team members have a solid foundation in digital circuit and FPGA design, as well as expertise in signal processing. They are fully capable of ensuring the smooth implementation of the project and ultimately completing the project. At the same time, the team members rely on the satellite navigation technology laboratory of the Communication Technology Research Institute of Harbin Institute of Technology, using the various hardware resources of the laboratory as the material guarantee of the project; the Communication Technology Research Institute started the satellite navigation technology as early as 10 years ago. Research has accumulated a large number of mature technologies.

In addition, the Virtex5 series of FPGAs have rich hardware resources, which are convenient for digital signal processing functions, can effectively realize large-scale FFT operations, and enable real-time frequency domain capture.

Project implementation plan

1. Basic functional block diagram and description

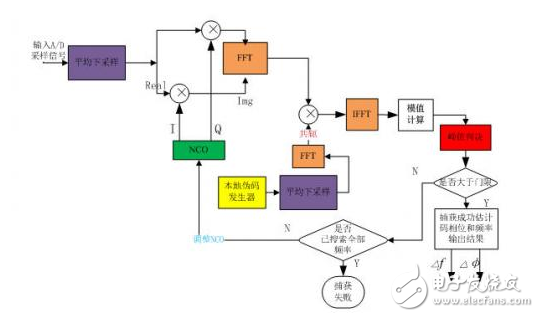

The scheme uses the FFT to perform a cyclic correlation operation between the received signal and the local signal in the frequency domain, so that the correlation values ​​of all code phases are simultaneously calculated, and the code phase delay of the received signal is estimated.

The specific process is as follows:

(1) The IF signal is sampled and then digitally down-converted. After average downsampling, the data is integrated and the number of points is matched. The matched data is passed to the FFT module. The I and Q branches perform complex FFT operations as the real and imaginary parts of the FFT, respectively.

(2) In the FFT unit, the incoming data is segmented, and the length L of the segment determines the length of the parallel operation, which has a great relationship with the capture probability and the capture time.

(3) For the locally generated spreading code, the FFT operation is performed after the average downsampling data is matched, and the complex conjugate is taken.

(4) Multiply the FFT result of the data segment and the address segment, and then perform an IFFT operation.

(5) Take the modulo value of the result of the IFFT and store the result.

(6) The result is captured and judged, and the maximum point in the frame after the accumulation is found to be compared with the set threshold. If it is higher than the threshold, a capture test is performed.

(7) If the threshold is lower than the threshold, adjust the NCO adjustment frequency and repeat the above steps.

2. Required development platform

The required development platform is XUPV5-LX110T, because the frequency domain acquisition algorithm requires large points of FFT transformation support.

3. Modules that need to be developed during the implementation of the solution

The frequency domain capture performed by this scheme is mainly divided into a top layer module, a down sampling module, an FFT module, a PRN sequence generation module, a complex multiplier module, an NCO module, a peak decision module, and a frequency search module.

4. The final performance metrics the system will achieve.

Under the condition that the SNR is -19dB, the pseudo code sequence is captured, and the estimation result of the code phase is within 0.5 chip range to meet the starting condition of the subsequent tracking module.

Other resources needed

1. Test Equipment

In the implementation of the program, Xilinx embedded logic analyzer; Spirent's navigation satellite signal source; Simulink and System generator are required.

2. Simulation, development tools

ISE integration platform, Matlab and simulink, System generator, Synplify Pro synthesis tool, and simulation tool Modelsim.

Our 12v battery pack designed to be chargeable via motorcycle/car cigaretter, capacity range from 2200mah to 10Ah, with wireless heat controller or bluetooth control. Applications widely ranges in heating clothing, heated motorcycle clothing, heated jacket, electric jacket, electric heated clothing, heated coat, heated vest, heated pants, heatgear, electric gloves, heated jacket mens, heated jacket womens.

12V Heated Jacket Battery,Heated Jacket Battery, Heated Coat Battery,Heated Vest Battery

Asarke Industry Co., Limited , https://www.asarke-industry.com